Birim devre tasarımı

Farklı tasarımlar oluşturmak için kendine benzeyen birimlerle devre tasarımı

Giriş

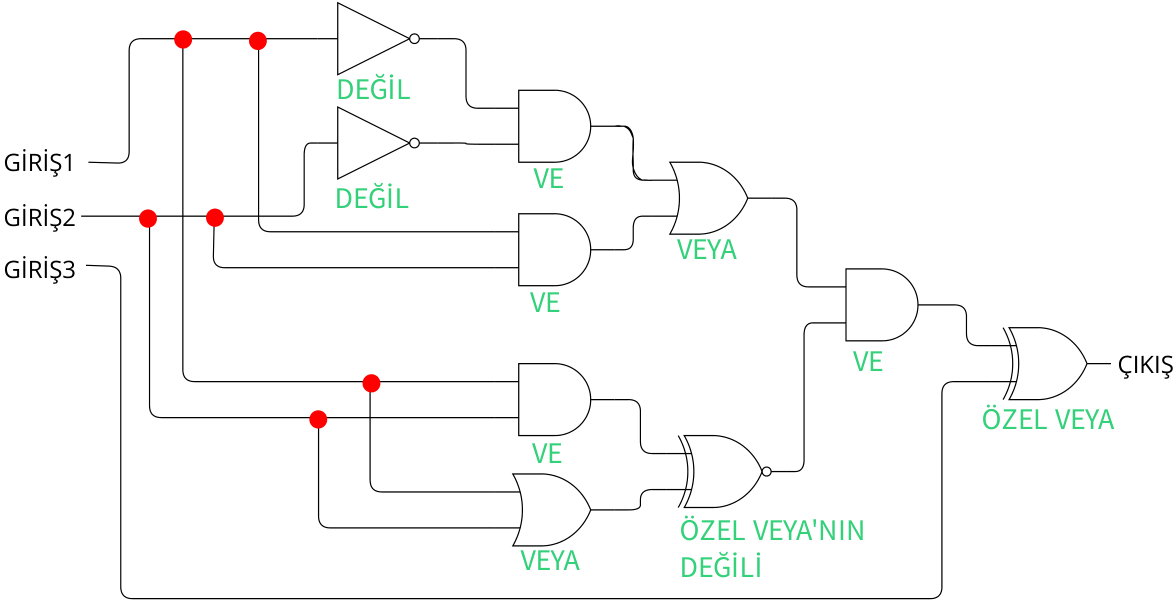

Bu bölümde farklı tasarımlar oluşturmak için kendine benzeyen başka birimlerle birleştirilebilen devre tasarımını inceleyeceğiz.

Devremiz ilk örneklere göre biraz daha karışık diyebiliriz.

Uygulamayı parçalara ayırıyoruz.

Böylece, 3 tane birim ve bu birimleri içeren bir ana birimimiz olmuş oldu.

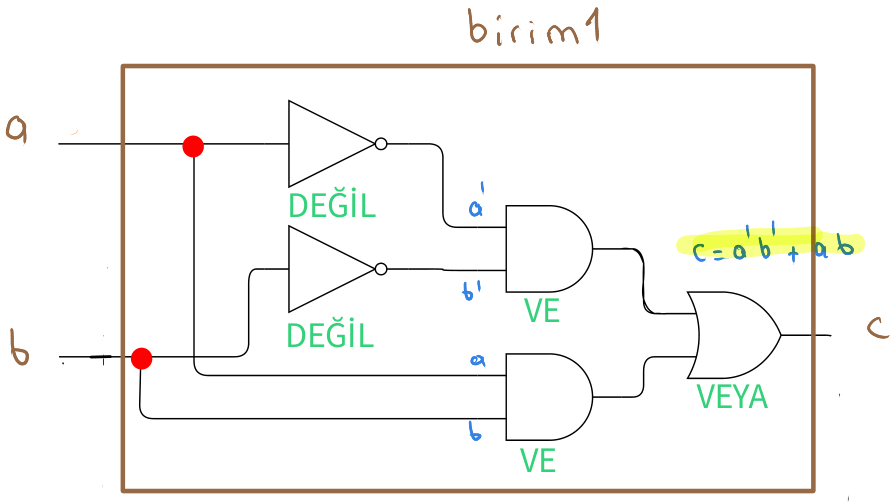

İlk birim

İlk birimin şemasını ve giriş çıkışlarını görebilirsiniz.

İlk birimi yazalım ve birim1.v ismi ile kaydedelim.

module birim1 (a, b, c);

input a, b;

output c;

assign c = (~a & ~b) | (a & b);

endmodule // birim1

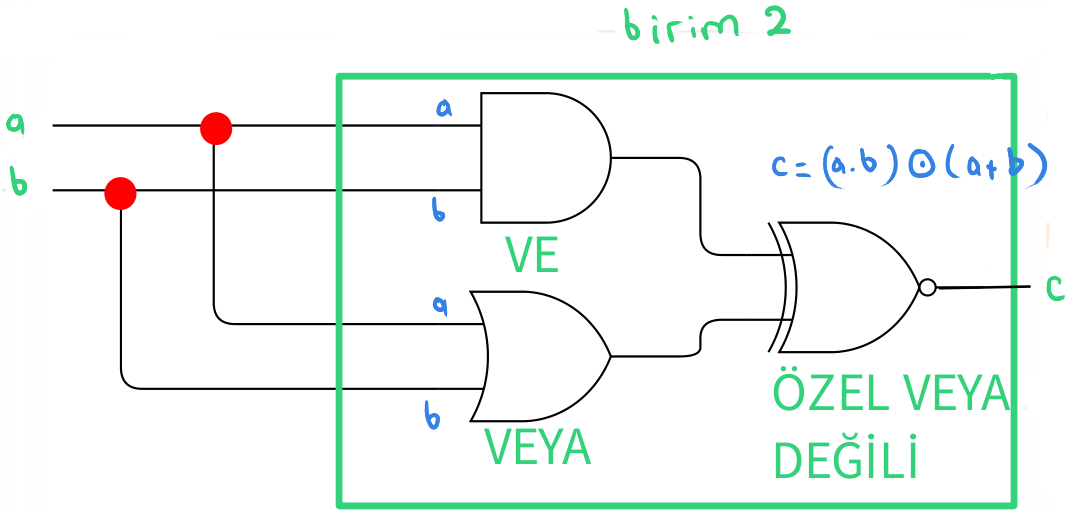

İkinci birim

İkinci birimin şemasını ve giriş çıkışlarını aşağıda görebilirsiniz.

İkinci birimi yazalım ve birim2.v ismi ile kaydedelim.

module birim2 (a, b, c);

input a, b;

output c;

assign c = ((a & b) ~^ (a | b));

endmodule // birim2

Burada & işlecinin VE , | işlecinin ise VEYA olduğunu zaten biliyorduk.

^ işleci kendi başına ÖZEL VEYA anlamına geliyor.

Örnekte olduğu gibi ~^ ile beraber kullanılırsa ÖZEL VEYA'NIN DEĞİLİ anlamına geliyor.

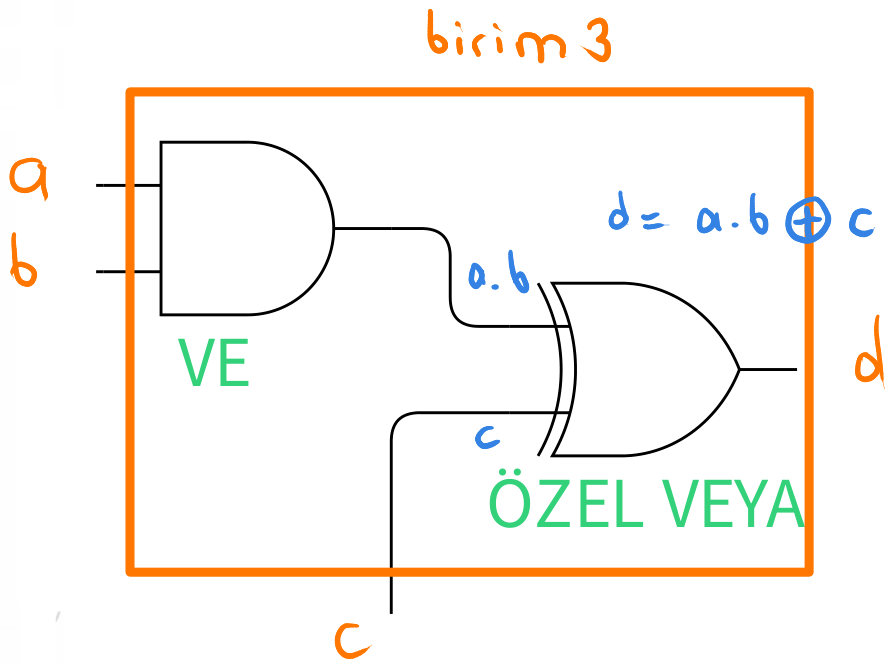

Üçüncü birim

Üçüncü birimin şemasını ve giriş çıkışlarını görebilirsiniz.

Üçüncü birimi yazalım ve birim3.v ismi ile kaydedelim.

module birim3 (a, b, c, d);

input a, b, c;

output d;

assign d = (a & b) ^ c;

endmodule // birim3

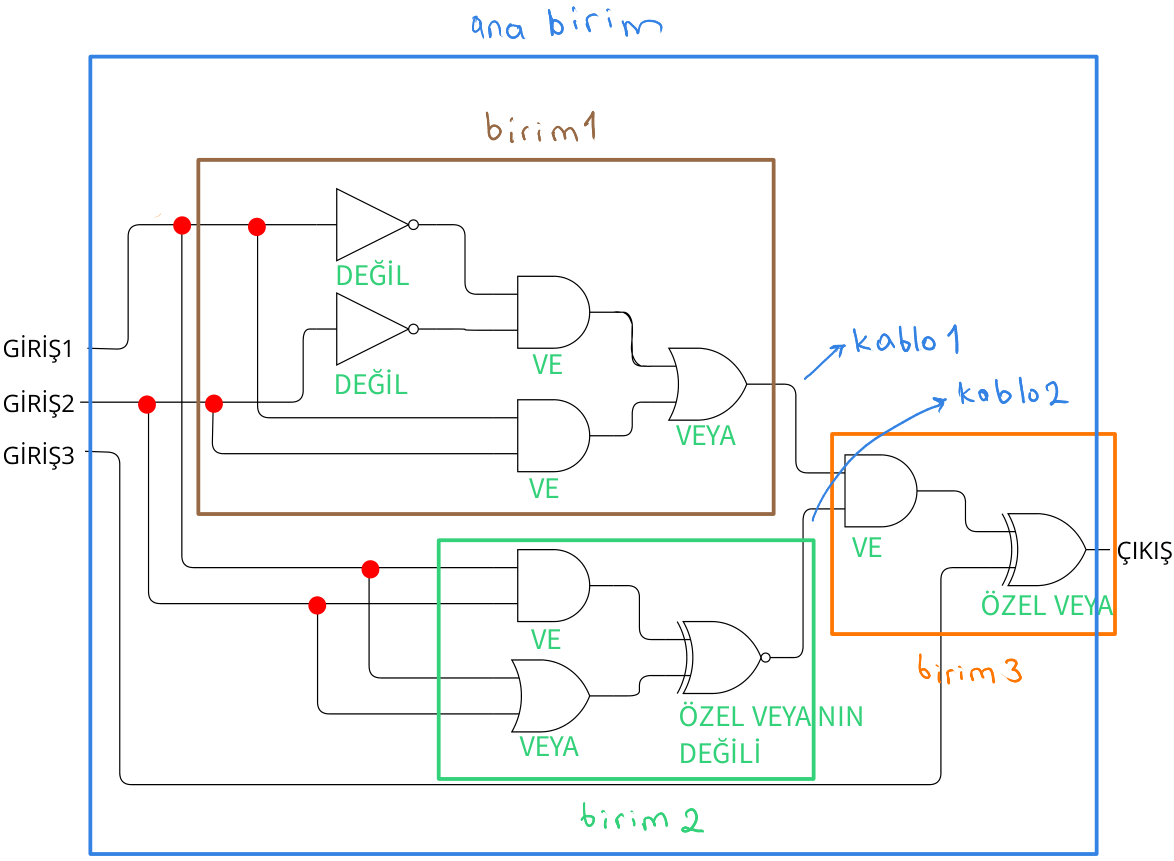

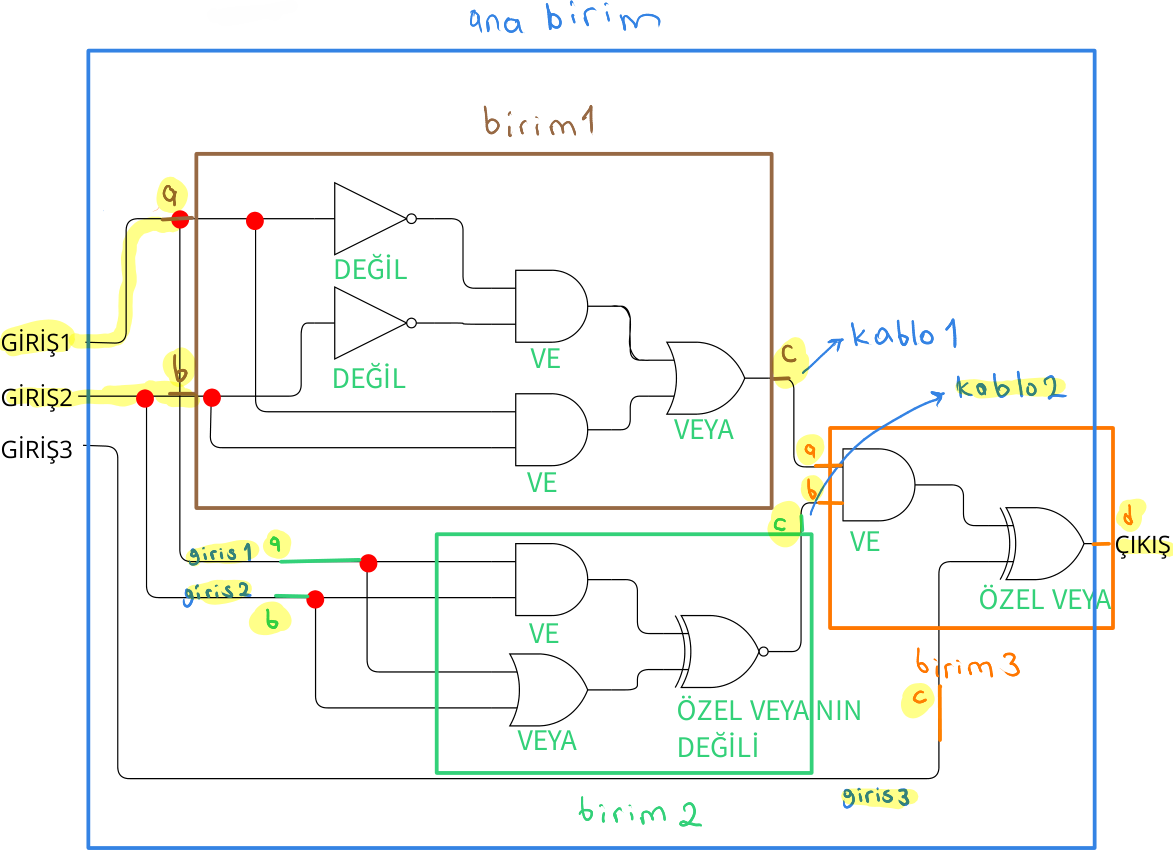

Ana birim

Devre şemasını, ana birimin diğer birimlerle bağlantılarını gösterecek şekilde düzenleyelim.

Ana birimi yazalım ve anabirim.v ismi ile kaydedelim.

module anabirim (giris1, giris2, giris3, cikis);

input giris1, giris2, giris3;

output cikis;

wire kablo1, kablo2;

birim1 ilk (.a(giris1), .b(giris2), .c(kablo1));

birim2 ikinci (.a(giris1), .b(giris2), .c(kablo2));

birim3 ucuncu (.a(kablo1), .b(kablo2), .c(giris3), .d(cikis));

endmodule // anabirim

Ana birimin açıklaması

Giriş, çıkış tanımlamalarına ek olarak burada wire ile iki kablo tanımlaması yapılmış.

İlk birim üzerinden gidersek, birim1'in giriş ve çıkışlarını anabirim'e bağlayacağız.

Ana birim içinde bu birime ilk diye yeni bir isim veriyoruz.

birim1 ilk (.a(giris1), .b(giris2), .c(kablo1)); ifadesinde ilk birimin a ve b girişlerini sırasıyla giris1 ve giris2'ye, c çıkışını ise kablo1'e bağlamak istediğimizi belirtiyoruz.

Diğer birimleri de benzer şekilde ana birime bağlıyoruz.

Deneme tezgahı

module anabirim_tezgah;

// Girişler

reg giris1;

reg giris2;

reg giris3;

// Çıkışlar

wire cikis;

// Test edilecekler

anabirim uut (

.giris1 (giris1),

.giris2 (giris2),

.giris3 (giris3),

.cikis (cikis)

);

initial begin

$dumpfile("anabirim.vcd");

$dumpvars(0,anabirim_tezgah);

// Girişleri ilklendir

giris1 = 0;

giris2 = 0;

giris3 = 0;

// 100 ns bekle

#100;

giris1 = 0;

giris2 = 0;

giris3 = 1;

// 10 ns bekle

#10;

giris1 = 0;

giris2 = 1;

giris3 = 0;

// 10 ns bekle

#10;

giris1 = 0;

giris2 = 1;

giris3 = 1;

// 10 ns bekle

#10;

giris1 = 1;

giris2 = 0;

giris3 = 0;

// 10 ns bekle

#10;

giris1 = 1;

giris2 = 0;

giris3 = 1;

// 10 ns bekle

#10;

giris1 = 1;

giris2 = 1;

giris3 = 0;

// 10 ns bekle

#10;

giris1 = 1;

giris2 = 1;

giris3 = 1;

// 10 ns bekle

#10;

end

endmodule // anabirim_tezgah

Deneme tezgahında üç giriş için tüm olasılıkları sınıyoruz.

Uygulamayı derlemek

Uygulama artık bir kaç kaynaktan oluştuğu için ufak bir make kütüğü yazabiliriz.

KAYNAK = anabirim.v \

anabirim_tezgah.v \

birim1.v \

birim2.v \

birim3.v \

all: anabirim

anabirim :

iverilog -o anabirim ${KAYNAK}

vvp anabirim

gtkwave anabirim.vcd &

temizle clean:

rm anabirim anabirim.vcd

Devre tasarımını derlemek için make komutu veriniz. Benzetim yazılımının başladığını görebilirsiniz.

Eğer anabirim'i ya da benzetim kütüğünü temizlemek isterseniz make temizle yazabilirsiniz.

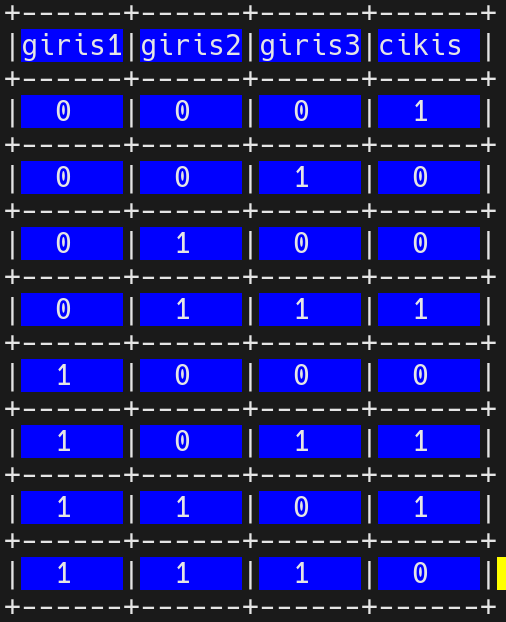

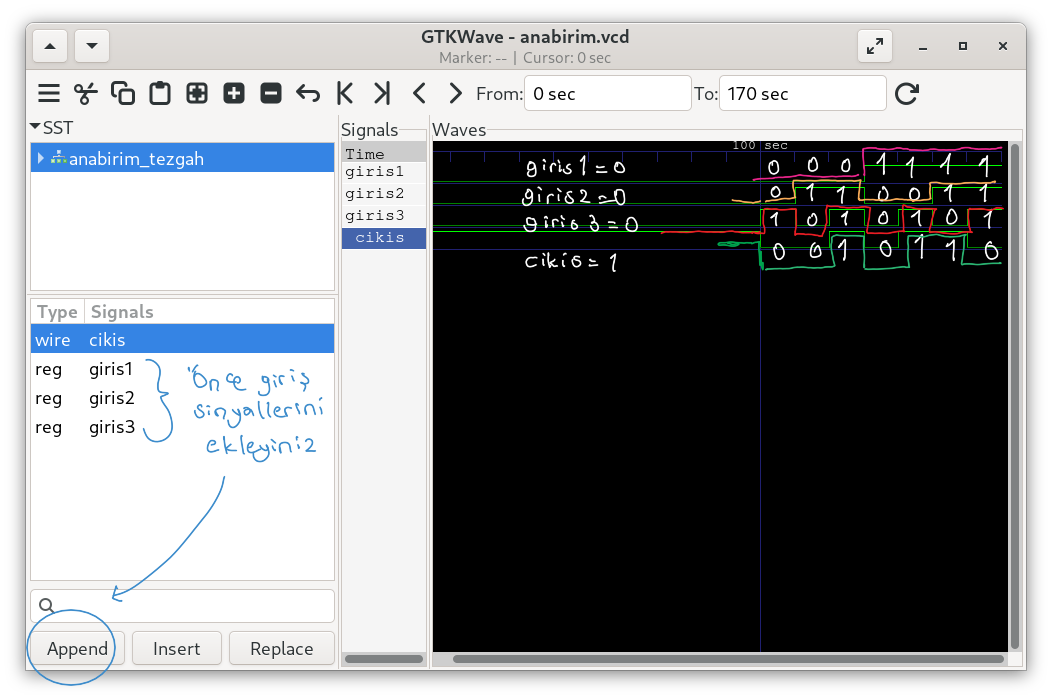

Benzetim sonuçlarının yorumlanması

Benzetim sonuçlarını yorumlamak için devrenin nasıl çalıştığını bilmemiz gerekir. Bunun için aşağıdaki doğruluk tablosundan yararlanabiliriz.

Benzetim sonuçlarına baktığımızda, devrenin olması gerektiği gibi çalıştığını görebiliyoruz.

Yorumlar