Özel veya kapısı

Bu derste verilog ile özel veya kapısı tasarımını anlatıyoruz.

Özel veya kapısı

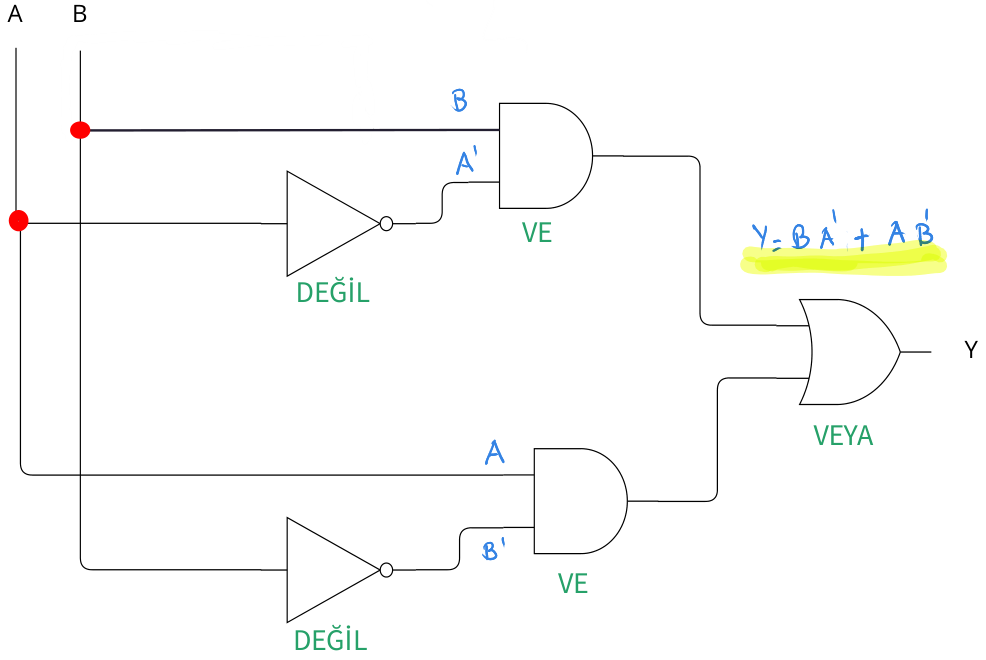

Öncelikle devremize bakalım.

Devrenin çıkışı Y yukarıda sarı ile vurgulanmış işlevi gerçekleştiriyor.

Bu kapıya özel veya "xor" kapısı deniliyor. Eğer A ve B farklı ise çıkışta 1 üretiyor, aynı ise çıkışta 0 veriyor.

Özel veya kapısı benzetimi

Devremiz sadece A ve B farklı ise çıkışta 1 veriyor.

Benzetim yazılımı üzerinde sınayabilirsiniz.

Özel veya işlevini yazalım

module ozelveya (a, b, y);

input a, b;

output y;

assign y = (~a & b) | (a & ~b);

endmodule // ozelveya

Bu kütüğü ozelveya.v ismi ile kaydedelim.

Özel veya açıklaması

Atama ifadesinde kullanılan ~ DEĞİL, & VE , | ise VEYA anlamına geliyor.

(~a & b) ifadesini A'NIN DEĞİLİ VE B diğerini ise (a & ~b) A VE B'NİN DEĞİLİ olarak okuyabiliriz.

Sonra bir | VEYA kapısı bu iki ifadeyi birbirine bağlıyor.

Sonucu da Y işlevine atıyoruz.

Özel veya sınama tezgahı

Bir tane kütük oluşturalım.

module ozelveya_tezgah;

// Girişler

reg a;

reg b;

// Çıkışlar

wire y;

// Test edilecekler

ozelveya uut (

.a (a),

.b (b),

.y (y)

);

initial begin

$dumpfile("ozelveya.vcd");

$dumpvars(0,ozelveya_tezgah);

// Girişleri ilklendir

a = 0;

b = 0;

// 100 ns bekle

#100;

a = 0;

b = 1;

// 10 ns bekle

#10;

a = 1;

b = 0;

// 10 ns bekle

#10;

a = 1;

b = 1;

// 10 ns bekle

#10;

end

endmodule // ozelveya_tezgah

Kütüğü ozelveya_tezgah.v olarak kaydedelim.

Sınama tezgahında diğer yaptığımız örnekten fazla bir değişiklik yok.

a 0 b 0,

a 0 b 1,

a 1 b 0,

a 1 b 1

olacak şekilde girişe farklı değerler veriyoruz.

Uygulamayı derleyelim

Uygulamayı derlemek için

iverilog -o ozelveya ozelveya.v ozelveya_tezgah.v

komutunu veriniz.

Benzetim kütüğünü oluşturmak için

vvp ozelveya

komutunu veriniz. Böylece ozelveya.vcd isimli bir benzetim kütüğü oluşacak.

Son olarak oluşan dalga şekline bakmak için

gtkwave ozelveya.vcd &

komutunu verebiliriz.

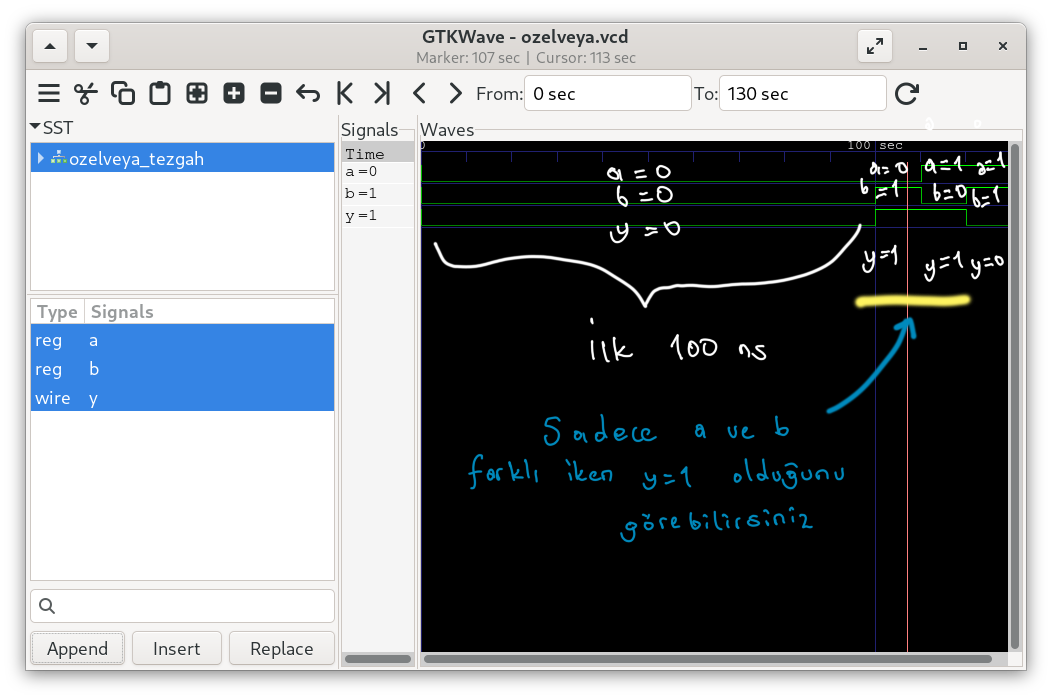

Benzetim sonuçları

Sol üstte bulunan ozelveya_tezgah yazan yere fare ile tıklayalım.

Fare ile işaretleri seçip ekle Append düğmesi ile ekleyelim.

Sadece a ve b farklı iken y = 1 olduğunu görebilirsiniz.

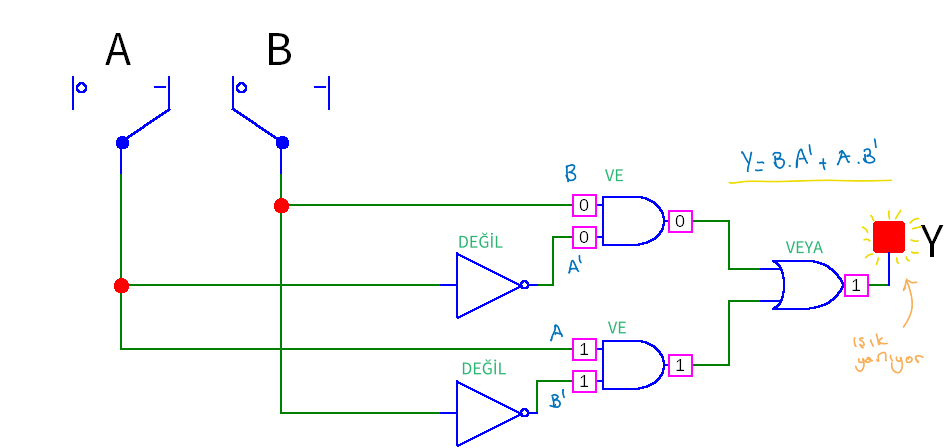

Devrenin Microcap ile benzetimi

Aşağıda aynı devrenin Microcap ile benzetimini görebilirsiniz.

Benzetim kütüğünü buradan indirebilirsiniz.

Benzetimi başlatmak için Analysis -> Dynamic DC seçmek yeterlidir.

Diğer yöntem

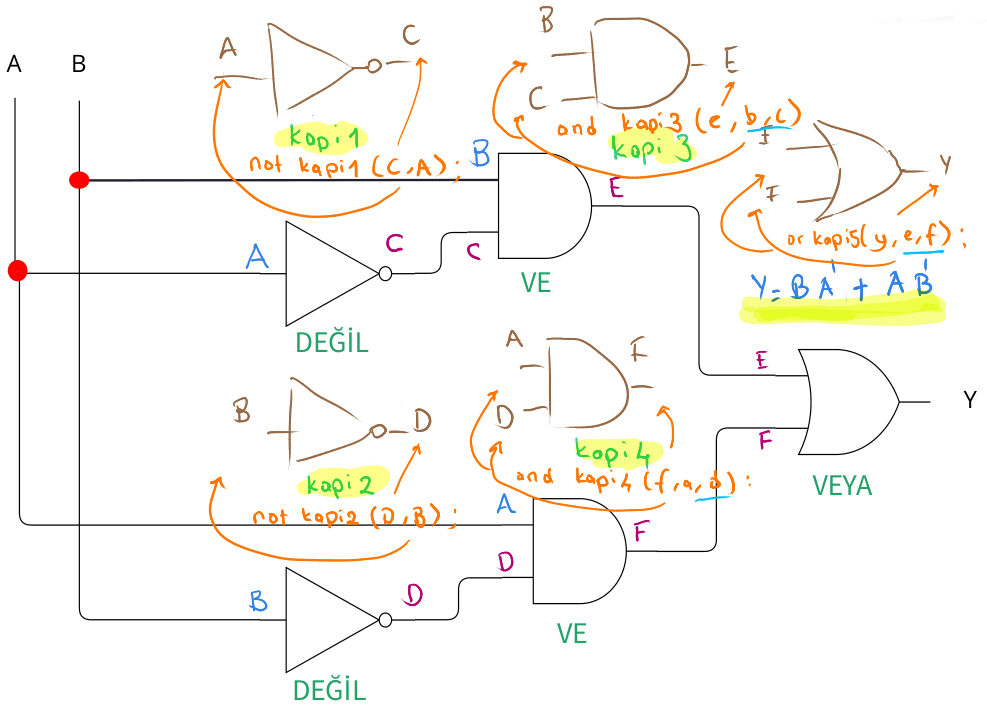

Öncelikle var olmayan girişleri C, D, E, F ekliyoruz.

Bu sefer aynı örneği kapılara bölerek tasarlayacağız.

Verilog kodu

module ozelveya2 (a, b, y);

input wire a, b;

output wire y;

wire c, d, e, f;

not kapi1 (c, a);

not kapi2 (d, b);

and kapi3 (e, b, c);

and kapi4 (f, a, d);

or kapi5 (y, e, f);

endmodule // ozelveya2

Kütüğü ozelveya2.v ismi ile kaydediniz.

Verilog kodunun açıklaması

Uygulamayı kapılara bölerek 5 tane kapı oluşturduk.

DEĞİL kapısı için not , VE kapısı için and , VEYA kapısı için ise or kullanıyoruz.

İlk kapıya bakarsak not kapi1 (c, a); ifadesinde, kapı isminden hemen sonra parantezler içerisine önce çıkışı, sonra girişi yazıyoruz.

Benzer şekilde üçüncü kapıya baktığımızda e'nin çıkış b ve c'nin giriş olarak tanımlandığını görebiliriz.

İkinci örnek için sınama tezgahı

module ozelveya2_tezgah;

// Girişler

reg a;

reg b;

// Çıkışlar

wire y;

// Test edilecekler

ozelveya2 uut (

.a (a),

.b (b),

.y (y)

);

initial begin

$dumpfile("ozelveya2.vcd");

$dumpvars(0,ozelveya2_tezgah);

// Girişleri ilklendir

a = 0;

b = 0;

// 100 ns bekle

#100;

a = 0;

b = 1;

// 10 ns bekle

#10;

a = 1;

b = 0;

// 10 ns bekle

#10;

a = 1;

b = 1;

// 10 ns bekle

#10;

end

endmodule // ozelveya2_tezgah

Kütüğü ozelveya2_tezgah.v ismi ile kaydediniz.

İkinci örneği derleyelim

İkinci örneği derlemek için

iverilog -o ozelveya2 ozelveya2.v ozelveya2_tezgah.v

komutunu veriniz.

Benzetim kütüğünü oluşturmak için

vvp ozelveya2

komutunu veriniz. Böylece ozelveya2.vcd isimli bir benzetim kütüğü oluşacak.

Son olarak oluşan dalga şekline bakmak için

gtkwave ozelveya2.vcd &

komutunu verebilirsiniz.

Yorumlar