Ve kapısı

Bu derste verilog ile ve kapısı tasarımını anlatacağız.

Giriş

Verilog elektronik tasarımında kullanılan bir donanım tanımlama dili.

Bu derste Linux altında verilog'a giriş yapacağız.

Bende FPGA kartı yok. Verilog derleyicisi ve benzetim yazılımından faydalanacağız.

Osman Tokluoğlu uygulamalı verilog dersleri hazırlamış. FPGA kartınız varsa ya da farklı işletim sistemi kullanıyorsanız bu dersleri takip edebilirsiniz.

Sayısal Elektronik konusunda ders almak ya da bilgilerinizi tazelemek isterseniz. Mehmet Burak Aykenar tarafından hazırlanan Mantıksal Devre Tasarımı derslerini takip edebilirsiniz.

Bazı devrelerin benzetimi Circuit Verse ile yapılmıştır.

Tüm benzetimlere buradan ulaşabilirsiniz.

Gerekli yazılımların kurulumu

Yazılım olarak verilog derleyicisine ve işaretleri çizmek için gtkwave yazılımına ihtiyacımız olacak.

Archlinux

sudo pacman -S iverilog gtkwave

komutu ile bu paketleri kurabilirsiniz.

Ubuntu

sudo apt install iverilog gtkwave

komutu ile bu paketleri kurabilirsiniz.

VE kapısı

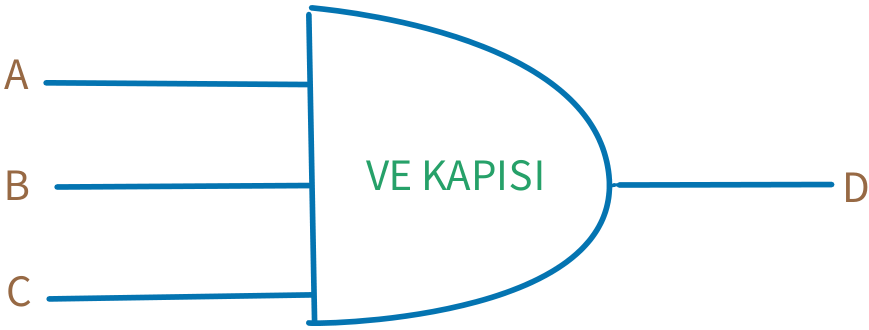

Verilog ile tasarlamayı düşündüğümüz 3 girişli VE kapısını görebilirsiniz.

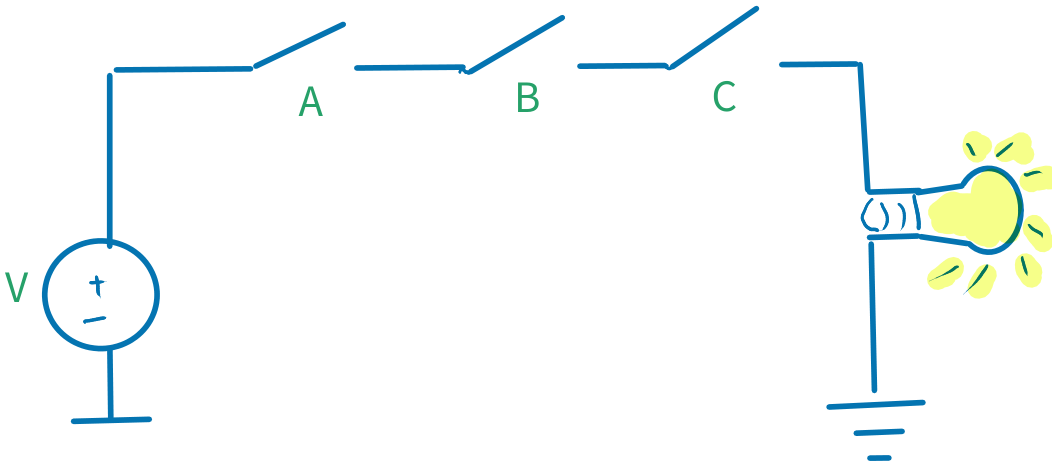

Öncelikle VE kapısının çalışma mantığını anlamakta fayda var. VE kapılarını seri bağlanmış anahtarlar gibi düşünebiliriz.

Resimden de görülebileceği gibi ışığın yanması için A, B ve C anahtarlarının 1 olması gerekiyor.

VE kapısı matematikte çarpma işlemine karşılık geliyor.

Ve kapısı benzetimi

Seri bağlı anahtar örneğinde olduğu gibi, çıkışın 1 olması için A, B ve C'nin 1 olması gerekiyor.

İlk verilog uygulaması

Herhangi bir metin düzenleyici ile bir kütük oluşturalım.

module vekapisi (a, b, c, d);

input a, b, c;

output d;

assign d = a & b & c;

endmodule // ve kapısı

Bu kütüğü vekapisi.v ismi ile kaydedelim.

İlk uygulamanın açıklaması

Uygulamayı module ve endmodule arasında yazıyoruz.

vekapisi uygulamanın ismini belirtiyor.

Parantezler içerisinde a, b, c ve d kapılarını kullanmak istediğimizi belirtiyoruz.

input a, b, c; ile a, b ve c kapılarını giriş olarak tanımlıyoruz.

output d; ile d kapısını çıkış olarak tanımlıyoruz.

assign d = a & b & c; ifadesinde assign d ile d kapısına bir değer atamak istediğimizi belirtiyoruz. Burada & işleci VE manasına geliyor.

Bir diğer ifadeyle d eşittir a VE b VE c olsun demek istiyoruz.

endmodule ile uygulamayı sonlandırıyoruz.

// işaretlerinden sonra girdiğimiz bilgiler yorum ya da açıklama olarak değerlendiriliyor.

İlk uygulama için sınama tezgahı

Tasarladığımız VE kapısı için bir sınama tezgahı yazmak istiyoruz.

VE kapısının girişine bazı değerler uygulayacağız. Çıkışta beklenen değerleri görüp, görmediğimizi sınayacağız.

Bunu bazı programlama dillerindeki birim testi gibi düşünebilirsiniz.

Metin düzenleyici ile kütüğün içine şunları girelim.

module vekapisi_tezgah;

// Girişler

reg a;

reg b;

reg c;

// Çıkışlar

wire d;

// Test edilecekler

vekapisi uut (

.a (a),

.b (b),

.c (c),

.d (d)

);

initial begin

$dumpfile("vekapisi.vcd");

$dumpvars(0,vekapisi_tezgah);

// Girişleri ilklendir

a = 0;

b = 0;

c = 0;

// 100 ns bekle

#100;

a = 1;

b = 1;

c = 0;

// 10 ns bekle

#10;

a = 1;

b = 1;

c = 1;

// 10 ns bekle

#10;

end

endmodule // vekapisi_tezgah

Bu kütüğü vekapisi_tezgah.v ismi ile kaydedelim.

Sınama tezgahının açıklaması

Sınama tezgahında initial begin ve end arasındaki ilklendirme bölümünü inceleyelim.

Benzetimi gösterebilmek için $dumpfile("vekapisi.vcd"); komutu ile bir kütük oluşturuyoruz.

Kütüğe kapı değerlerini yazmak için $dumpvars(0,vekapisi_tezgah); kullanıyoruz.

Devamında girişleri ilklendiren bölümü görüyoruz.

// Girişleri ilklendir

a = 0;

b = 0;

c = 0;

// 100 ns bekle

#100;

Sisteme güç verdikten sonra cihaz kararlı hale gelene kadar yaklaşık 100 ns kadar bekliyoruz.

Asıl sınama bölümünü bundan sonra yazıyoruz.

a = 1;

b = 1;

c = 0;

// 10 ns bekle

#10;

a 1, b 1 ve c 0 iken sonuç ne olacak bunu göster diyoruz. #10 ifadesi ise 10 ns kadar bekle diyor.

Üstte VE kapısının açıklamalarında a 1, b 1 ve c 1 iken çıkışta 1 görebileceğimizi ifade etmiştik.

Bir sonraki bölümde de a 1, b 1 ve c 1 iken sonucu göster diyoruz.

Uygulamayı derleyelim

Uygulamayı derlemek için

iverilog -o vekapisi vekapisi.v vekapisi_tezgah.v

komutunu veriniz.

Benzetim kütüğünü oluşturmak için

vvp vekapisi

komutunu veriniz. Böylece vekapisi.vcd isimli bir benzetim kütüğü oluşacak.

Son olarak oluşan dalga şekline bakmak için

gtkwave vekapisi.vcd &

komutunu verebiliriz.

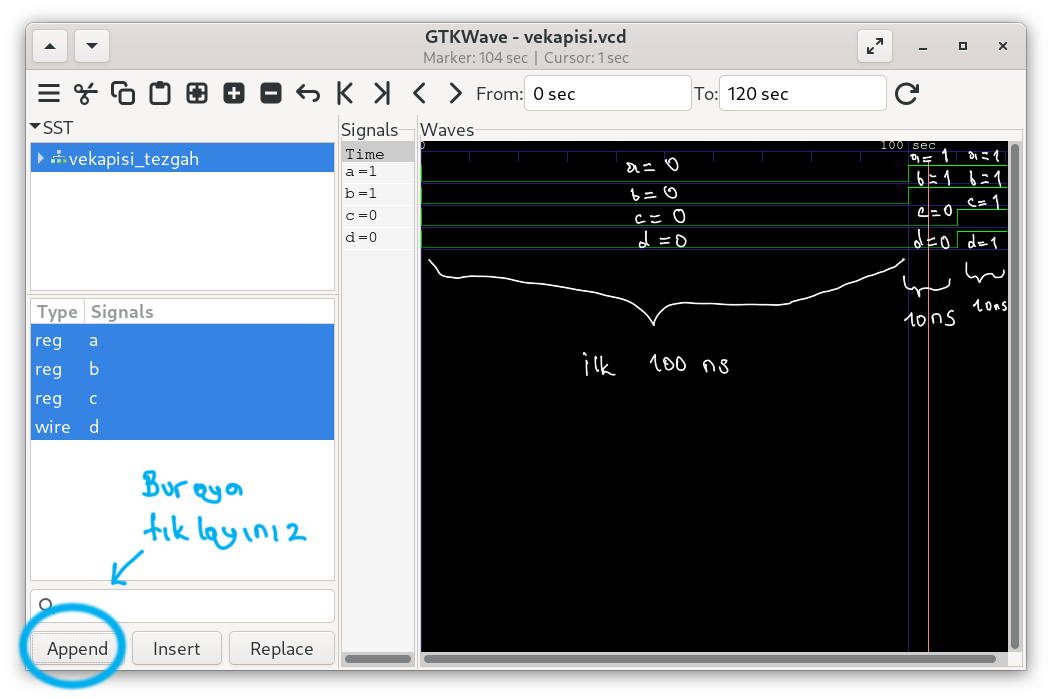

Benzetim sonuçları

Açılan pencerede sol üst köşede vekapisi_tezgah yazan yere fare ile tıklayınız.

Alt kısımda giriş ve çıkış kapılarını görebilirsiniz.

Fare ile bunların hepsini seçip ekle Append düğmesine tıklayalım.

Benzetim sonuçlarına bakarsanız, uygulamanın beklenildiği gibi çalıştığını görebilirsiniz.

Yorumlar