Yarım toplayıcı tam toplayıcı

Yarım toplayıcı ve tam toplayıcı tasarımı

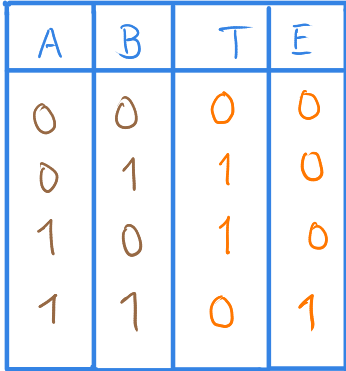

Yarım toplayıcı doğruluk tablosu

A ve B isminde iki tane girişimiz olsun. Doğruluk tablosunu yukarıda görebilirsiniz.

Eğer A 0 ve B 1 ise T (toplam) 1 oluyor.

Eğer A 1 ve B 0 ise T (toplam) gene 1 oluyor.

Eğer A 1 ve B 1 ise T (toplam) 2 oluyor.

İkilik sayı sisteminde işlem yaptığımız için 0 yazıyoruz. E (elde) 1 oluyor.

Yukarıda doğruluk tablosu gösterilen devreye yarım toplayıcı deniliyor.

İki yarım toplayıcı kullanarak, bir tam toplayıcı yapılabiliyor.

Yarım toplayıcı devre şeması

Doğruluk tablosunu kullanarak yarım toplayıcının devre şemasını çıkarabiliriz.

T için düşünürsek T'nin 1 olduğu alanları yuvarlak içine alıyoruz.

İlk ifadeyi baktığımızda A 0 olduğu için DEĞİL'ini alıyoruz. B 1 olduğu için aynen yazıyoruz.

Böylece ifadenin ilk kısmı A'nın DEĞİLİ VE B oldu.

Alttaki satırda A 1 olduğu için aynen yazıyoruz. B 0 olduğu için DEĞİL'ini alıyoruz.

İfadenin ikinci kısmı A VE B'nin DEĞİLİ oldu.

Son olarak bu iki ifadeyi VEYA ile birleştiriyoruz.

Böylece T ifadesi (A'nın DEĞİLİ VE B) VEYA (A VE B'nin DEĞİLİ) oldu.

Dikkat ederseniz bulduğumuz T ifadesi A ve B farklı iken çıkışta 1 veriyor. Bu işlevin devre karşılığı ÖZEL VEYA kapısıdır.

ÖZEL VEYA kapısı girişler farklı ise çıkışta 1 verir.

E'ye baktığımızda E'nin 1 olduğu alanları yuvarlak içine alıyoruz.

Hem A hem de B 1 olduğu için ifademiz A VE B oldu.

Elde işlemi için bir tane VE kapısı kullanmak yeterli olacaktır.

Yarım toplayıcı benzetim

Devrenin benzetimini aşağıda bulabilirsiniz.

Yarım toplayıcı

Aşağıdaki örnekte yarım toplayıcıyı dallanma kullanarak yazdık.

module yarimtoplayici (a, b, t, e);

input a, b;

output reg t, e;

always @ (a, b) begin

if ((a == 0) & (b == 0)) begin

t <= 0;

e <= 0;

end

else if ((a == 0) & (b == 1)) begin

t <= 1;

e <= 0;

end

else if ((a == 1) & (b == 0)) begin

t <= 1;

e <= 0;

end

else if ((a == 1) & (b == 1)) begin

t <= 0;

e <= 1;

end

end

endmodule // yarimtoplayici

Yarım toplayıcıyı yazdıktan sonra yarimtoplayici.v ismi ile kaydedelim.

Yarım toplayıcı açıklama

always bloğunun içerisindeki çıkışlarını yazmaç reg olarak tanımlamak gerekiyor..

always @ (a, b) kullanımında, sadece a ve b değeri değiştiğinde always bloğu içerisini çalıştır diyoruz.

Parantezler içerisinde yalnız a olduğunu düşünelim. Bu durumda, sadece a girişi değiştiğinde always bloğu çalıştırılacaktı.

a ve b sıfır iken t ve e sıfır oluyor.

t <= 0;

e <= 0;

ifadesindeki <= işleci t ve e değişkenlerine aynı anda değer ataması yapıldığını gösteriyor.

Yarım toplayıcı sınama tezgahı

module yarimtoplayici_tezgah;

// Girişler

reg a;

reg b;

// Çıkışlar

wire t;

wire e;

// Test edilecekler

yarimtoplayici uut (

.a (a),

.b (b),

.t (t),

.e (e)

);

initial begin

$dumpfile("yarimtoplayici.vcd");

$dumpvars(0,yarimtoplayici_tezgah);

// Girişleri ilklendir

a = 0;

b = 0;

// 100 ns bekle

#100;

a = 0;

b = 1;

// 10 ns bekle

#10;

a = 1;

b = 0;

// 10 ns bekle

#10;

a = 1;

b = 1;

// 10 ns bekle

#10;

end

endmodule // yarimtoplayici_tezgah

Kütüğü yarimtoplayici_tezgah.v ismi ile kaydediniz.

Yarım toplayıcıyı derleyelim

Yarım toplayıcıyı derlemek için

iverilog -o yarimtoplayici yarimtoplayici.v yarimtoplayici_tezgah.v

komutunu veriniz.

Benzetim kütüğünü oluşturmak için

vvp yarimtoplayici

komutunu veriniz. Böylece yarimtoplayici.vcd isimli bir benzetim kütüğü oluşacak.

Son olarak oluşan dalga şekline bakmak için

gtkwave yarimtoplayici.vcd &

komutunu verebilirsiniz.

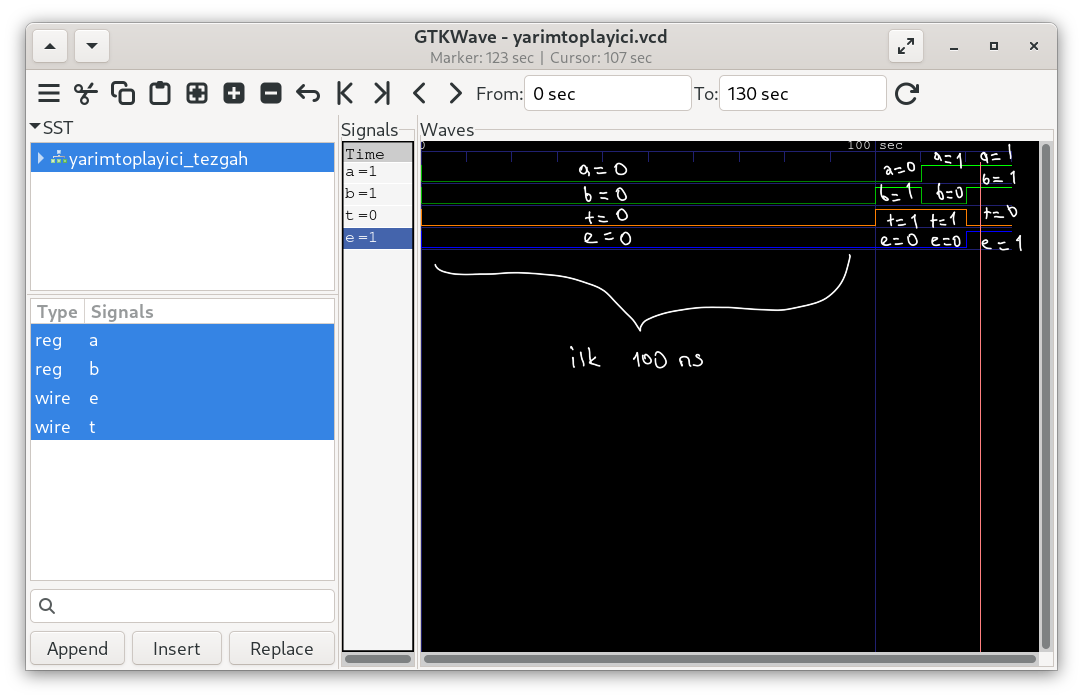

Yarım toplayıcı benzetim sonuçları

Benzetim sonuçlarına baktığımızda, devrenin beklendiği gibi çalıştığını görebiliriz.

Devre şemasını kullanarak yarım toplayıcı

Aynı örneği devre şemasını kullanarak yazabiliriz.

module yarimtoplayici2 (a, b, t, e);

input a, b;

output t, e;

assign t = a ^ b;

assign e = a & b;

endmodule // yarimtoplayici2

Kütüğü yarimtoplayici2.v ismi ile kaydediniz

Yukarıdaki örnekte ^ işleci ÖZEL VEYA , & ise VE anlamına geliyor.

Devre şeması kullanan yarım toplayıcı için sınama tezgahı

module yarimtoplayici2_tezgah;

// Girişler

reg a;

reg b;

// Çıkışlar

wire t;

wire e;

// Test edilecekler

yarimtoplayici2 uut (

.a (a),

.b (b),

.t (t),

.e (e)

);

initial begin

$dumpfile("yarimtoplayici2.vcd");

$dumpvars(0,yarimtoplayici2_tezgah);

// Girişleri ilklendir

a = 0;

b = 0;

// 100 ns bekle

#100;

a = 0;

b = 1;

// 10 ns bekle

#10;

a = 1;

b = 0;

// 10 ns bekle

#10;

a = 1;

b = 1;

// 10 ns bekle

#10;

end

endmodule // yarimtoplayici2_tezgah

Kütüğü yarimtoplayici2_tezgah.v ismi ile kaydediniz.

Sınama tezgahının, ilk örnekten isimlendirme dışında farkı yok.

Eğer arzu ederseniz, derleyip benzetim sonuçlarına bakabilirsiniz.

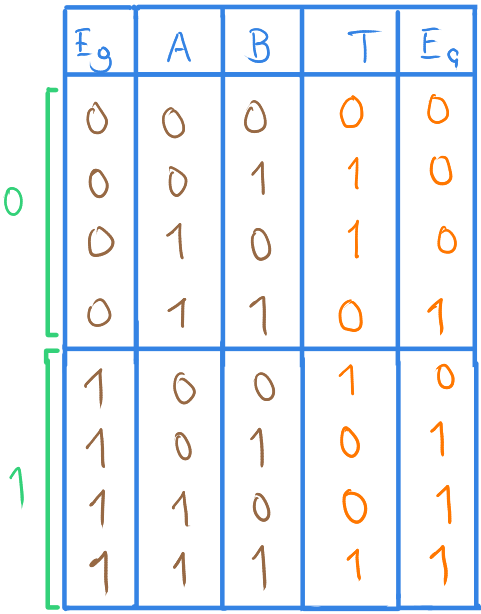

Tam toplayıcı doğruluk tablosu

Tam toplayıcı doğruluk tablosuna baktığımızda hem Eg elde girişi, hem de Eç elde çıkışı olduğunu görüyoruz.

Elde girişi 0 iken, tam toplayıcı doğruluk tablosunun üst kısmının yarım toplayıcı doğruluk tablosu ile aynı olduğunu görebilirsiniz.

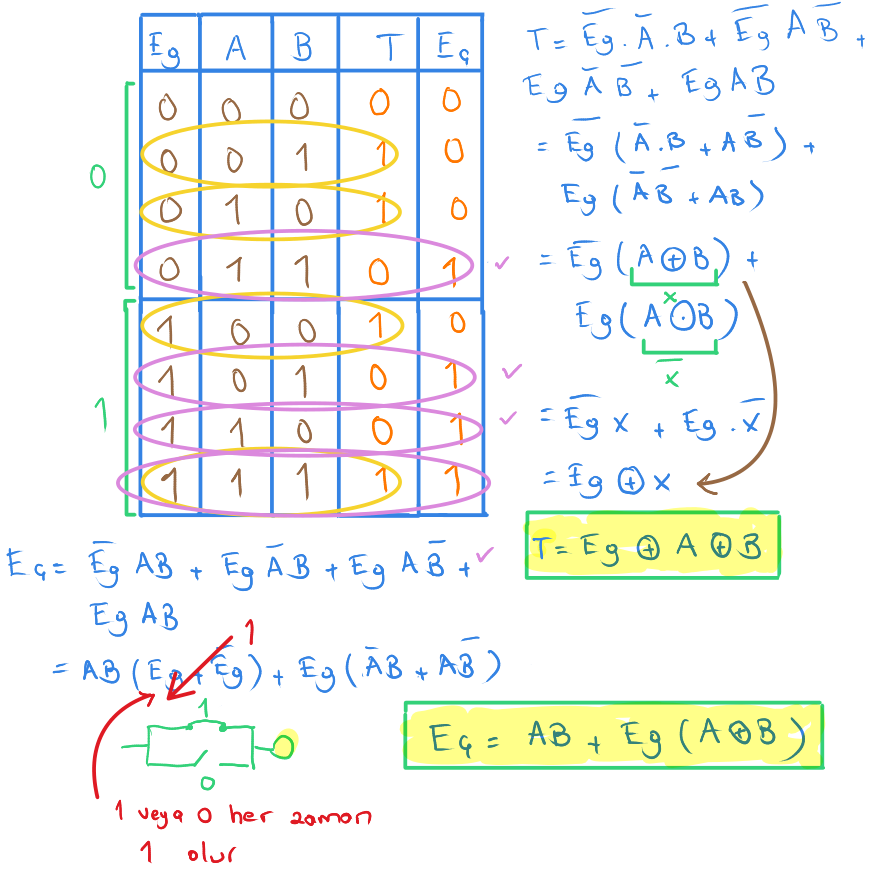

Doğruluk tablosundan işlevleri hesaplayalım

Doğruluk tablosunu kullanarak toplam T ve Eç elde çıkışı hesaplayabiliriz.

Toplam ve elde çıkış hesaplanırken yapılan sadeleştirmeleri aşağıdaki resimde görebilirsiniz.

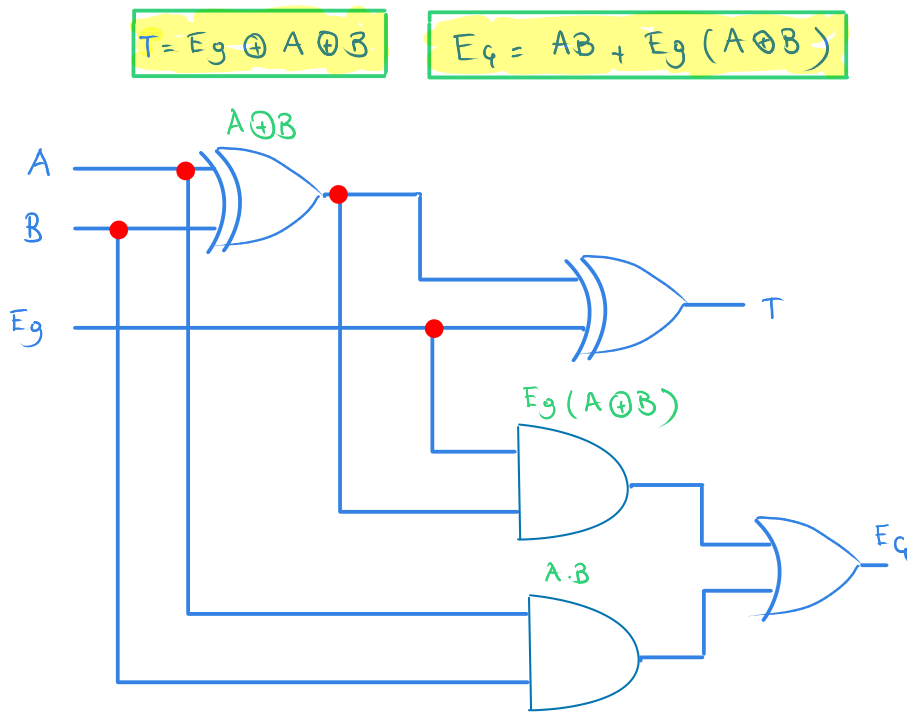

Tam toplayıcı devre şeması

Artık elimizde toplam ve elde çıkış işlevleri olduğu için devre şemasını kolaylıkla çizebiliriz.

Tam toplayıcı benzetim

Tam toplayıcı benzetimini aşağıda bulabilirsiniz.

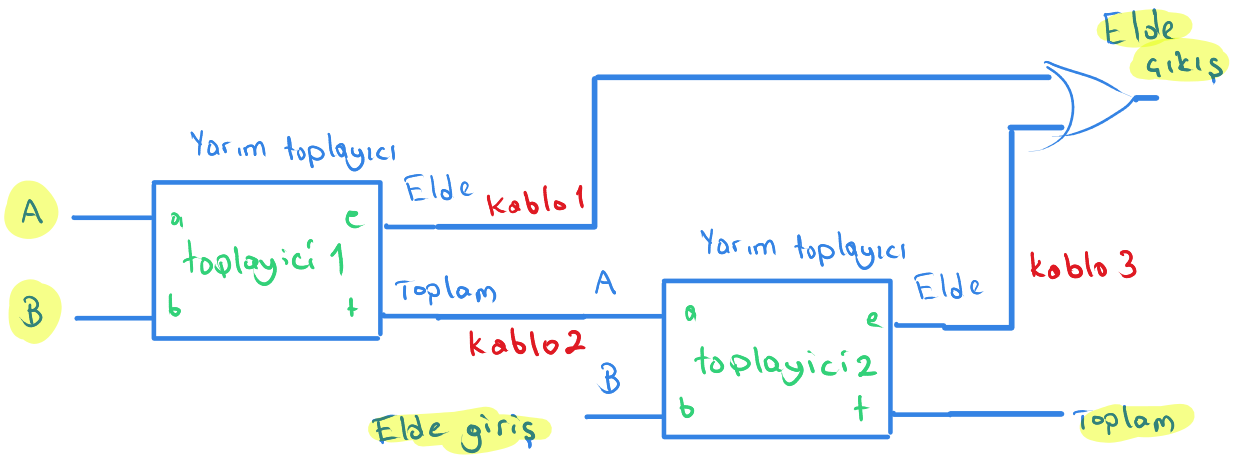

Dersin başında iki yarım toplayıcıdan bir tam toplayıcı yapılabileceğinden bahsetmiştik.

Bunu örnekleyen bir devreyi aşağıda bulabilirsiniz.

Devre şeması kullanarak tam toplayıcı

module tamtoplayici (a, b, eldegiris, toplam, eldecikis);

input a, b, eldegiris;

output toplam, eldecikis;

assign toplam = (a ^ b) ^ eldegiris;

assign eldecikis = (a & b) | (eldegiris & (a ^ b));

endmodule // tamtoplayici

Kütüğü tamtoplayici.v ismi ile kaydediniz.

Tam toplayıcı deneme tezgahı

module tamtoplayici_tezgah;

// Girişler

reg a;

reg b;

reg eldegiris;

// Çıkışlar

wire toplam;

wire eldecikis;

// Test edilecekler

tamtoplayici uut (

.a (a),

.b (b),

.eldegiris (eldegiris),

.toplam (toplam),

.eldecikis (eldecikis)

);

initial begin

$dumpfile("tamtoplayici.vcd");

$dumpvars(0,tamtoplayici_tezgah);

// Girişleri ilklendir

a = 0;

b = 0;

eldegiris = 0;

// 100 ns bekle

#100;

a = 0;

b = 1;

eldegiris = 0;

// 10 ns bekle

#10;

a = 1;

b = 0;

eldegiris = 0;

// 10 ns bekle

#10;

a = 1;

b = 1;

eldegiris = 0;

// 10 ns bekle

#10;

a = 0;

b = 0;

eldegiris = 1;

// 10 ns bekle

#10;

a = 0;

b = 1;

eldegiris = 1;

// 10 ns bekle

#10;

a = 1;

b = 0;

eldegiris = 1;

// 10 ns bekle

#10;

a = 1;

b = 1;

eldegiris = 1;

// 10 ns bekle

#10;

end

endmodule // tamtoplayici_tezgah

Kütüğü tamtoplayici_tezgah.v ismi ile kaydediniz.

Tam toplayıcıyı derleyelim

Tam toplayıcıyı derlemek için

iverilog -o tamtoplayici tamtoplayici.v tamtoplayici_tezgah.v

komutunu veriniz.

Benzetim kütüğünü oluşturmak için

vvp tamtoplayici

komutunu veriniz. Böylece tamtoplayici.vcd isimli bir benzetim kütüğü oluşacak.

Son olarak oluşan dalga şekline bakmak için

gtkwave tamtoplayici.vcd &

komutunu verebilirsiniz.

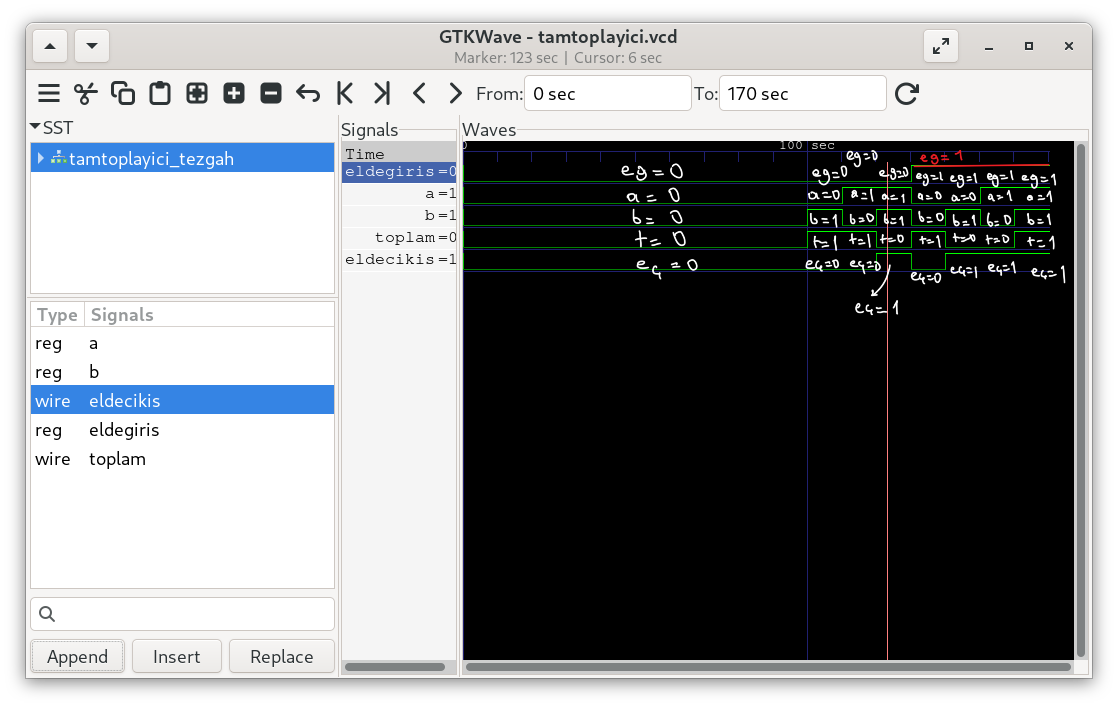

Benzetim sonuçları

Benzetim sonuçlarından, devrenin olması gerektiği gibi çalıştığını görülebilir.

İki yarım toplayıcıdan tam toplayıcı

Tasarımı birimlere ayırarak iki tane yarım toplayıcıdan bir tam toplayıcı yapabiliriz.

Herhangi bir metin düzenleyici ile bir kütük oluşturalım.

module tamtoplayici2 (a, b, eldegiris, toplam, eldecikis);

input a, b, eldegiris;

output toplam, eldecikis;

wire kablo1, kablo2, kablo3;

yarimtoplayici2 toplayici1 (.a(a), .b(b), .e(kablo1), .t(kablo2));

yarimtoplayici2 toplayici2 (.a(kablo2), .b(eldegiris), .e(kablo3), .t(toplam));

assign eldecikis = kablo1 | kablo3;

endmodule // tamtoplayici2

Kütüğü tamtoplayici2.v ismi ile kaydedelim.

module tamtoplayici2_tezgah;

// Girişler

reg a;

reg b;

reg eldegiris;

// Çıkışlar

wire toplam;

wire eldecikis;

// Test edilecekler

tamtoplayici2 uut (

.a (a),

.b (b),

.eldegiris (eldegiris),

.toplam (toplam),

.eldecikis (eldecikis)

);

initial begin

$dumpfile("tamtoplayici2.vcd");

$dumpvars(0,tamtoplayici2_tezgah);

// Girişleri ilklendir

a = 0;

b = 0;

eldegiris = 0;

// 100 ns bekle

#100;

a = 0;

b = 1;

eldegiris = 0;

// 10 ns bekle

#10;

a = 1;

b = 0;

eldegiris = 0;

// 10 ns bekle

#10;

a = 1;

b = 1;

eldegiris = 0;

// 10 ns bekle

#10;

a = 0;

b = 0;

eldegiris = 1;

// 10 ns bekle

#10;

a = 0;

b = 1;

eldegiris = 1;

// 10 ns bekle

#10;

a = 1;

b = 0;

eldegiris = 1;

// 10 ns bekle

#10;

a = 1;

b = 1;

eldegiris = 1;

// 10 ns bekle

#10;

end

endmodule // tamtoplayici2_tezgah

Sınama tezgahını da tamtoplayici2_tezgah.v olarak kaydediniz.

Uygulamayı derlemek için

iverilog -o tamtoplayici2 tamtoplayici2.v yarimtoplayici2.v tamtoplayici_tezgah2.v

komutunu veriniz.

Daha sonra

vvp tamtoplayici2

ile benzetim kütüğünü oluşturabilirsiniz.

Benzetim sonuçlarına bakmak için

gtkwave tamtoplayici2.vcd &

komutunu veriniz.

Yorumlar