Yosys kurulumu

Yosys, Verilog kaynak kodunun tasarımını gösterebiliyor.

Yosys kurulumu

Archlinux

sudo pacman -S yosys xdot

komutu ile gerekli paketleri kurabilirsiniz.

Yosys kullanımı

Yosys için, üzerinde deneme yapacağımız bazı verilog kütüklerine ihtiyacımız olacak.

Bunun için ilk verilog dersinde oluşturduğumuz ve kapısını kullanabiliriz.

Öncelikle vekapisi isminde boş bir dizin oluşturuyoruz.

Herhangi bir metin düzenleyici ile bir kütük oluşturalım.

module vekapisi (a, b, c, d);

input a, b, c;

output d;

assign d = a & b & c;

endmodule // ve kapısı

Bu kütüğü vekapisi.v ismi ile kaydedelim.

Bir kütük daha oluşturalım.

read -sv vekapisi.v

hierarchy -top vekapisi

proc; opt

show

write_verilog üretilen.v

İçerisine yukarıdaki bilgileri girdikten sonra üret.ys olarak kaydedelim.

Böylece verilog kaynak kodundan tasarımı oluşturacak bir betik oluşturduk.

Betiğin açıklaması

Betiğin ilk satırı verilog kaynak kodundan okuyor.

İkinci satırda en üst birimi vekapisi olarak belirliyoruz.

Üçüncü satır always satırlarını bağlanabilir öğelere dönüştürüyor ve bazı en iyileştirmeler yapıyor.

Dördüncü satırda tasarımı xdot ile görebiliyoruz.

Son satır oluşturulan bağları yeni bir verilog kütüğüne yazıyor.

Yosys'yi çalıştıralım

yosys üret.ys

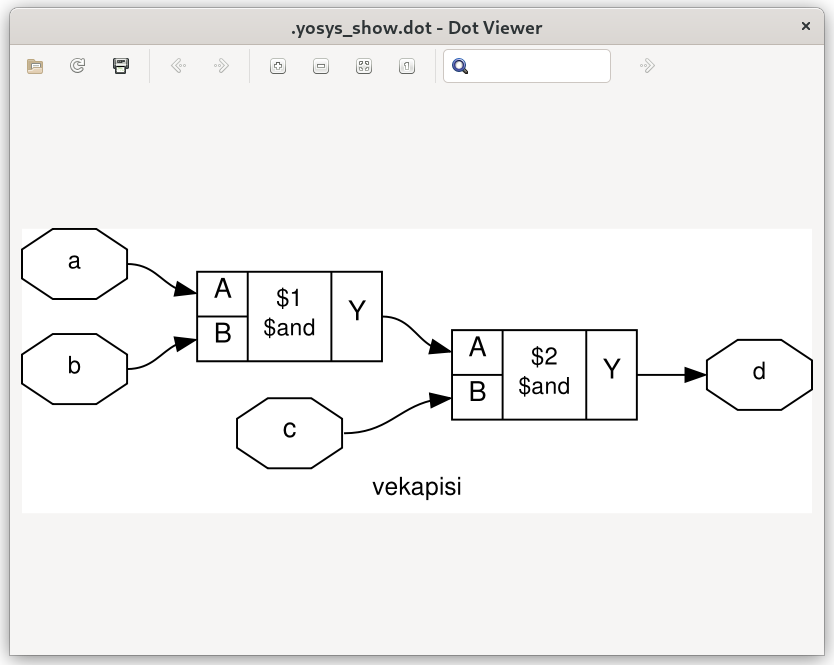

Sonuca baktığımızda ilk tasarımımızda elemanlar arası bağların oluşturulduğunu görebiliyoruz.

Başka bir örnek

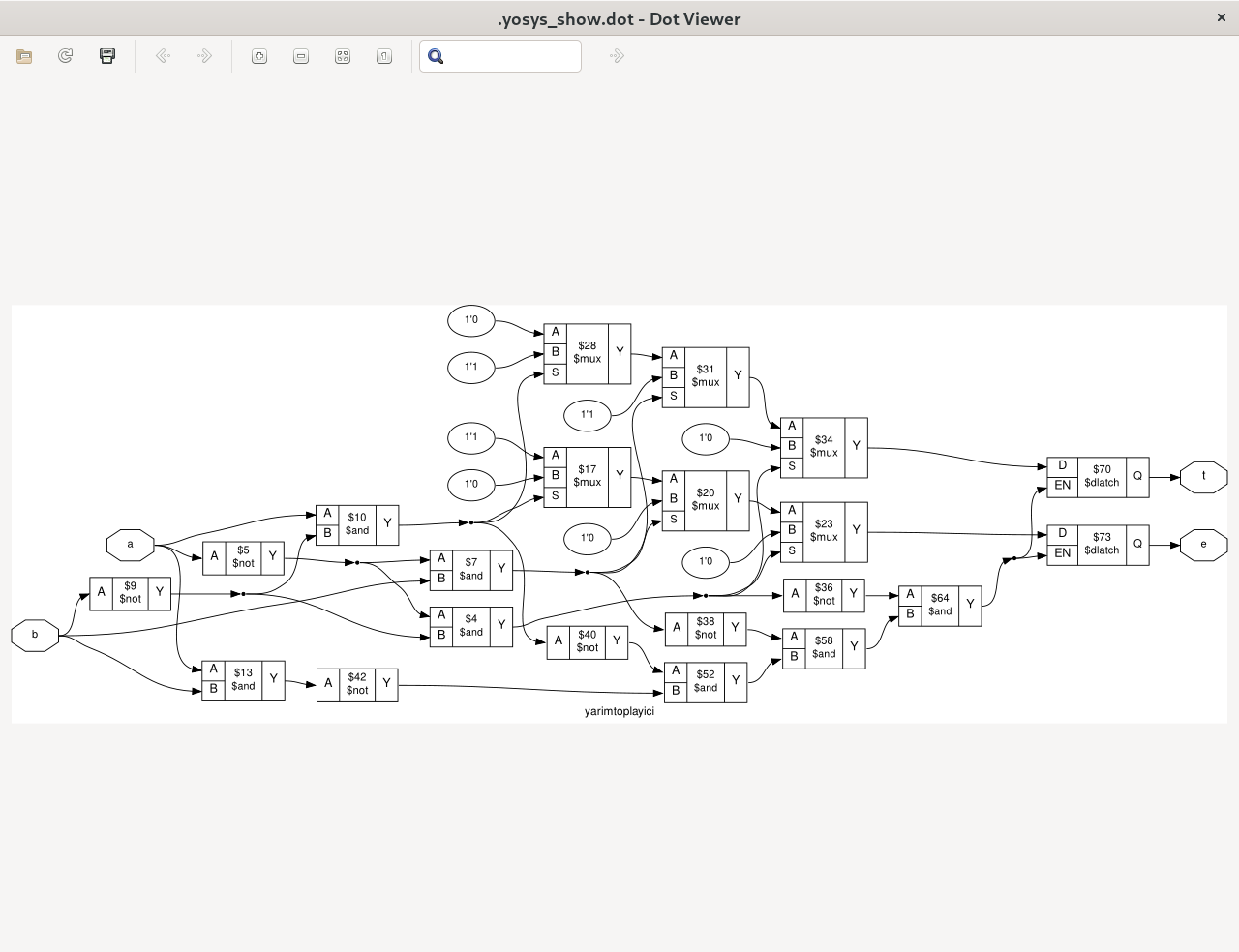

İlk yazdığımız dallanma kullanan yarım toplayıcı için üretilen bağlara bakarsak oldukça karışık olduğunu görebiliyoruz.

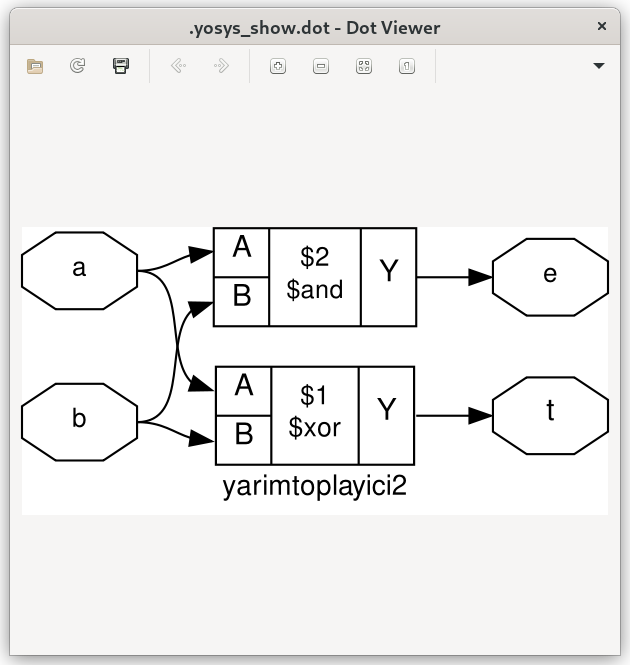

Devre şeması kullanan yarım toplayıcı için üretilen bağlara bakarsanız aradaki farkı görebilirsiniz.

Yorumlar